# On-Chip Power Distribution Grids With Multiple Supply Voltages for High-Performance Integrated Circuits

Mikhail Popovich, Member, IEEE, Eby G. Friedman, Fellow, IEEE, Michael Sotman, and Avinoam Kolodny, Member, IEEE

Abstract-On-chip power distribution grids with multiple supply voltages are discussed in this paper. Two types of interdigitated and paired power distribution grids with multiple supply voltages and multiple grounds are presented. Analytic models are also developed to estimate the loop inductance in four types of proposed power delivery schemes. Two proposed schemes, fully and pseudo-interdigitated power delivery, reduce power supply voltage drops as compared to conventional interdigitated power distribution systems with dual supplies and a single ground by, on average, 15.3% and 0.3%, respectively. The performance of the proposed on-chip power distribution grids is compared to a reference power distribution grid with a single supply and a single ground. The voltage drop in fully interdigitated and fully paired power distribution grids with multiple supplies and multiple grounds is reduced, on average, by 2.7% and 2.3%, respectively, as compared to the voltage drop of an interdigitated power distribution grid with a single supply and a single ground. The proposed power distribution grids are a better alternative to a single supply voltage and a single ground power distribution system. On-chip resonances in power distribution grids with decoupling capacitors are intuitively explained in this paper, and circuit design implications are provided. It is also noted that fully interdigitated and fully paired power distribution grids with multiple supply voltages and multiple grounds are recommended to decouple power supply voltages.

*Index Terms*—Decoupling capacitors, multiple power supply voltages, on-chip resonances, power distribution networks, power grids.

### I. INTRODUCTION

ITH the on-going miniaturization of integrated circuit (IC) feature size, the design of power and ground distribution networks has become a challenging task. These challenges arise from shorter rise/fall times, lower noise

Manuscript received July 6, 2006; revised January 5, 2007 and January 25, 2007. This work was supported in part by the Semiconductor Research Corporation under Contract 2004-TJ-1207, the National Science Foundation under Contracts CCR-0304574 and CCF-0541206, grants from the New York State Office of Science, Technology and Academic Research to the Center for Advanced Technology in Electronic Imaging Systems, and grants from Intel Corporation, Eastman Kodak Company, Intrinsix Corporation, and Freescale Semiconductor Corporation.

M. Popovich is with CDMA Technologies, Qualcomm Corporation, San Diego, CA 92121 USA (e-mail: mikhailp@qualcomm.com).

E. G. Friedman is with the Department of Electrical and Computer Engineering, University of Rochester, Rochester, NY 14627 USA (e-mail: friedman@ece.rochester.edu).

M. Sotman was with the Department of Electrical Engineering, Israel Institute of Technology, Haifa, 32000 Israel. He is now with Intel Corporation, Israel Development Center, Haifa, Israel (e-mail: michael.sotman@intel.com).

A. Kolodny is with the Department of Electrical Engineering, Israel Institute of Technology, Haifa, 32000 Israel (e-mail: kolodny@ee.technion.ac.il).

Digital Object Identifier 10.1109/TVLSI.2008.2000515

margins, higher currents, and increased current densities. Furthermore, the power supply voltage has decreased to lower dynamic power dissipation. A greater number of transistors increases the total current drawn from the power supply. Simultaneously, the higher switching speed of a greater number of smaller transistors produces faster and larger current transients in the power distribution network [1]. The higher currents produce large IR voltage drops. Fast current transients lead to large  $L \ di/dt$  inductive voltage drops ( $\Delta I$  noise) within the power distribution networks.

The lower voltage of the power supply level can be described as

$$V_{\text{load}} = V_{\text{dd}} - IR - L\frac{dI}{dt} \tag{1}$$

where  $V_{\text{load}}$  is the voltage level seen from a current load,  $V_{\text{dd}}$  is the power supply voltage, I is the current drawn from the power supply, R and L are the resistance and inductance of the power distribution network, respectively, and dt is the rise time of the current drawn by the load. The power distribution networks should be designed to minimize voltage fluctuations, maintaining the power supply voltage as seen from the load within specified design margins (typically  $\pm 5\%$  of the power supply level). If the power supply voltage drops too low, the performance and functionality of the circuit will be severely compromised. Excessive overshoots of the supply voltage can also affect circuit reliability and should therefore be reduced.

With a new era of nanometer-scale CMOS circuits, power dissipation has become perhaps the critical design criterion. To manage the problem of high power dissipation, multiple on-chip power supply voltages have become commonplace [2]. This strategy has the advantage of permitting those modules along the critical paths to operate with the highest available voltage level (in order to satisfy target timing constraints) while permitting modules along the noncritical paths to use a lower voltage (thereby reducing energy consumption). In this manner, the energy consumption is decreased without affecting circuit speed. This scheme is used to enhance speed in a smaller area as compared to the use of parallel architectures. Using multiple supply voltages for reducing power requirements has been investigated in the area of high level synthesis for low power [3], [4]. While it is possible to provide multiple supply voltages, in practical applications such a scenario is expensive. Practically, a small number of voltage supplies (two or three) can be effective [5].

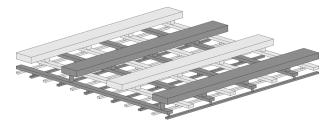

Power distribution networks in high-performance ICs are commonly structured as a multilayer grid [6]. In such a grid, straight power/ground lines in each metalization layer can span

Fig. 1. Multilayer on-chip power distribution grid [7]. The ground lines are light grey, the power lines are dark grey. The signal lines are not shown.

an entire die and are orthogonal to the lines in adjacent layers. Power and ground lines typically alternate in each layer. Vias connect a power (ground) line to another power (ground) line at the overlap sites. A typical on-chip power grid is illustrated in Fig. 1, where three layers of interconnect are depicted with the power lines shown in dark grey and the ground lines shown in light grey.

An on-chip power distribution grid in modern high-performance ICs is a complex multilevel system. The design of on-chip power distribution grids with multiple supply voltages is the primary focus of this paper. The paper is organized as follows. Existing work on power distribution grids and related power distribution systems with multiple supply voltages is reviewed in Section II. The structure of a power distribution grid and the simulation setup are reviewed in Section III. The structure of a power distribution grid with dual supply voltages and dual grounds (DSDG) is proposed in Section IV. Interdigitated power distribution grids with DSDG are described in Section V. Paired power distribution grids with DSDG are analyzed in Section VI. Simulation results are presented in Section VIII. Circuit design implications are discussed in Section VIII. Some specific conclusions are summarized in Section IX.

#### II. BACKGROUND

On-chip power distribution grids have traditionally been analyzed as purely resistive networks [8]. In this early work, a simple model is presented to estimate the maximum on-chip IR drop as a function of the number of metal layers and the metal layer thickness. The optimal thickness of each layer is shown to produce minimum IR drops. Design techniques are provided to maximize the available signal wiring area while maintaining a constant IR drop. These guidelines, however, have limited application to modern, high complexity power distribution networks. The inductive behavior of the on-chip power distribution networks has been neglected because the network inductance has been to date dominated by the off-chip parasitic inductance of the package. With the introduction of advanced packaging techniques and the increased switching speed of integrated circuits, this situation has changed. As noted in [9], by replacing wider power and ground lines with narrower interdigitated power and ground lines, the partial self-inductance of the power supply network can be reduced. The authors in [10] propose replacing the wide power and ground lines with an array of interdigitated narrow power and ground lines to decrease the characteristic impedance of the power grid. The dependence of the characteristic impedance on the separation between the

metal lines and the metal ground plane is considered. The application of the proposed power delivery scheme, however, is limited to interdigitated structures.

Several design methodologies using multiple power supply voltages have been described in the literature. A row by row optimized power supply scheme, providing a different supply voltage to each cell row, is described in [11]. The original circuit is partitioned into two subcircuits by conventional layout methods. Another technique, presented in [12], decreases the total length of the on-chip power and ground lines by applying a multiple supply voltage scheme. A layout architecture exploiting multiple supply voltages in cell-based arrays is described in [13]. Three different layout architectures are analyzed. The authors show that the power consumed by an IC can be reduced, albeit with an increase in area. In previously reported publications, only power distribution systems with two power supply voltages and one common ground have been described. On-chip power distribution grids with multiple power supply voltages and multiple grounds are proposed in this paper.

### **III. SIMULATION SETUP**

The inductance extraction program FastHenry [14] is used to analyze the inductive properties of the on-chip power grids. FastHenry efficiently calculates the frequency dependent self and mutual impedances,  $R(\omega) + \omega L(\omega)$ , in complex three-dimensional interconnect structures. A magneto-quasistatic approximation is utilized, meaning the distributed capacitance of the line and any related displacement currents associated with the capacitances are ignored. The accelerated solution algorithm employed in FastHenry provides approximately a 1% worst case accuracy as compared to directly solving the system of linear equations characterizing the structure.

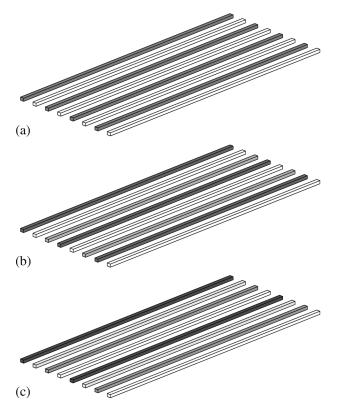

Copper is assumed as the interconnect material with a conductivity of  $(1.72 \ \mu\Omega \cdot cm)^{-1}$ . A line thickness of 1  $\mu$ m is assumed for each of the lines in the grids. In the analysis, the lines are split into multiple filaments to account for the skin affect. The number of filaments are estimated to be sufficiently large to achieve a 1% accuracy. Simulations are performed assuming a 1-GHz signal frequency (modeling the low-frequency case) and a 100-GHz signal frequency (modeling the high-frequency case). The interconnect structures are composed of interdigitated and paired power and ground lines. Three different types of interdigitated power distribution grids are shown in Fig. 2. The total number of lines in each power grid is 24. Each of the lines is incorporated into a specific power distribution network and distributed equally between the power and ground networks. The maximum simulation time is under five minutes on a Sun Blade 100 workstation.

# IV. POWER DISTRIBUTION GRID WITH DUAL SUPPLY AND DUAL GROUND

Multiple power supply voltages have been widely used in modern high-performance ICs, such as microprocessors, to decrease power dissipation. Only power distribution schemes with dual supply voltages and a single ground (DSSG) have been reported in the literature [6], [11]–[13], [15], [16]. In these networks, both power supplies share the one common ground. The

Fig. 2. Interdigitated power distribution grids under investigation. In all of the power distribution structures, the power lines are interdigitated with the ground lines. (a) A reference power distribution grid with a single supply voltage and a single ground (SSSG). The power lines are grey colored and the ground lines are white colored. (b) A power distribution grid with DSSG. The power lines are light and dark grey colored and the ground lines are white colored. (c) The proposed power distribution grid with DSDG. The power lines are shown in black and dark grey colors and the ground lines are shown in white and light grey colors.

ground bounce produced by one of the power supplies therefore adds to the power noise in the other power supply. As a result, voltage fluctuations are significantly increased. To address this problem, an on-chip power distribution scheme with DSDG is proposed. In this way, the power distribution system consists of two independent power delivery networks.

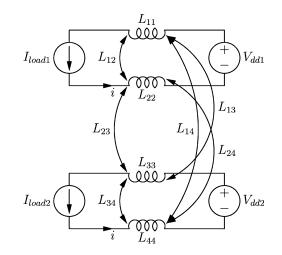

A power distribution grid with DSDG consists of two separate subnetworks with independent power and ground supply voltages and current loads. No electrical connection exists between the two power delivery subnetworks. In such a structure, the two power distribution systems are only coupled through the mutual inductance of the ground and power paths, as shown in Fig. 3.

The loop inductance of the current loop formed by the two parallel paths is

$$L_{\text{loop}} = L_{\text{pp}} + L_{\text{gg}} - 2M \tag{2}$$

where  $L_{pp}$  and  $L_{gg}$  are the partial self-inductances of the power and ground paths, respectively, and M is the mutual inductance between these paths. The current in the power and ground lines is assumed to always flow in opposite directions (a reasonable and necessary assumption in large power grids). The inductance of the current loop formed by the power and ground lines is therefore reduced by 2M. The loop inductance of the power

Fig. 3. Circuit diagram of the mutual inductive coupling of the proposed power distribution grid.  $L_{11}$  and  $L_{33}$  denote the partial self-inductances of the power lines and  $L_{22}$  and  $L_{44}$  denote the partial self-inductances of the ground lines, respectively.

distribution grid can be further reduced by increasing the mutual inductive coupling between the power and ground lines. As described by Rosa in 1908 [17], the mutual inductance between two parallel straight lines of equal length is

$$M_{\text{loop}} = 0.2l \left( \ln \frac{2l}{d} - 1 + \frac{d}{l} - \ln \gamma + \ln k \right) \mu \text{H} \quad (3)$$

where l is the line length, and d is the distance between the line centers. This expression is valid for the case where  $l \gg d$ . The mutual inductance of two straight lines is a weak function of the distance between the lines [6].

Analogous to inductive coupling between two parallel loop segments, as described in [18], the mutual loop inductance of the two power distribution grids with DSDG is

$$M_{\rm loop} = L_{13} - L_{14} + L_{24} - L_{23}.$$

(4)

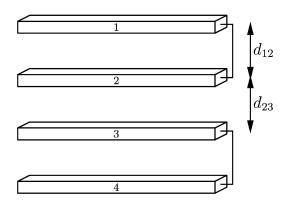

Note that the two negative signs before the mutual inductance components in (4) correspond to the current in the power and ground paths flowing in opposite directions. Also note that since the mutual inductance M in (2) is negative,  $M_{\text{loop}}$  should be negative to lower the loop inductance. If  $M_{\text{loop}}$  is positive, the mutual inductive coupling between the power/ground paths is reduced and the effective loop inductance is therefore increased. If the distance between the lines making a loop is much smaller than the separation between the two loops,  $L_{13} \approx L_{14}$  and  $L_{23} \approx L_{24}$ . This situation is the case for paired power distribution grids. In such grids, the power and ground lines are located in pairs in close proximity. For the interdigitated grid structure shown in Fig. 2(c), the distance between the lines  $d_{12}$  is the same as an offset between the two loops  $d_{23}$ , as illustrated in Fig. 4. In this case, assuming  $d_{12} = d_{23} = d$ , from (3),  $M_{\text{loop}}$  between the two grids is approximately

$$M_{\rm loop} = 0.2l \ln \frac{3}{4} \mu \text{H.}$$

<sup>(5)</sup>

Thus, the  $M_{\text{loop}}$  between the two grids is negative (with an absolute value greater than zero) in DSDG grids. The loop in-

Fig. 4. Physical structure of an interdigitated power distribution grid with DSDG. The proposed power delivery scheme consists of two independent power delivery networks.

$$L_{\parallel} = \frac{L_{\rm pp}^{1} L_{\rm pp}^{2} - M^{2}}{L_{\rm pp}^{1} + L_{\rm pp}^{2} - 2M}$$

(6)

where  $L_{\rm pp}^1$  and  $L_{\rm pp}^2$  are the partial self-inductance of the two power paths, respectively, and M is the mutual inductance between these paths. The mutual inductance between the two loops is therefore increased. Thus, the loop inductance seen from a particular current load increases, producing larger power/ground L di/dt voltage fluctuations.

### V. INTERDIGITATED GRIDS WITH DSDG

As shown in Section IV, by utilizing the power distribution scheme with DSDG, the loop inductance of the particular power delivery network is reduced. In power distribution grids with DSDG, the mutual inductance M between the power and ground paths in (2) includes two terms. One term accounts for the increase (or decrease) in the mutual coupling between the power and ground paths in the particular power delivery network due to the presence of the second power delivery network. The other term is the mutual inductance in the loop formed by the power and ground paths of the particular power delivery network. Thus, the mutual inductance in power distribution grids with DSDG is

$$M = M' + M_{\text{loop}} \tag{7}$$

where M' is the mutual inductance in the loop formed by the power and ground lines of the particular power delivery network and  $M_{\text{loop}}$  is the mutual inductance between the two power delivery networks. M' is always negative.  $M_{\text{loop}}$  can be either negative or positive.

The loop inductance of a conventional interdigitated power distribution grid with DSSG has recently been compared to the loop inductance of an example interdigitated power distribution grid with DSDG [19]. In general, multiple interdigitated power

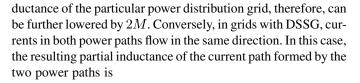

Fig. 5. Physical structure of a fully interdigitated power distribution grid with DSDG. The distance between the lines making the loops  $d_I^i$  is equal to the separation between the two loops  $s_I^i$ .

distribution grids with DSDG can be utilized, satisfying different design constraints in high-performance ICs. Exploiting the symmetry between the power supply and ground networks, all of the possible interdigitated power distribution grids with DSDG can be characterized by two primary power delivery schemes. Two types of interdigitated power distribution grids with DSDG are described in this section. The loop inductance in the first type of power distribution grids is presented in Section V-A. The loop inductance in the second type of power distribution grids is discussed in Section V-B.

# A. Type I Interdigitated Grids With DSDG

In the first type of interdigitated power distribution grids, the power and ground lines in each power delivery network and in different voltage domains (power and ground supply voltages) are alternated and equidistantly spaced, as shown in Fig. 5. These power distribution grids are described here as *fully inter-digitated* power distribution grids with DSDG.

Consistent with (4), the mutual inductive coupling of two current loops in fully interdigitated grids with DSDG is

$$M_{\text{loop}}^{\text{intI}} = L_{\text{Vdd1-Vdd2}} - L_{\text{Vdd1-Gnd2}} + L_{\text{Gnd1-Gnd2}} - L_{\text{Vdd2-Gnd1}}$$

(8)

where  $L_{ij}$  is the mutual inductance between the power and ground paths in the two power distribution networks. In general, a power distribution grid with DSDG should be designed to ensure that  $M_{\text{loop}}$  is negative with the maximum possible absolute value. Alternatively,

$$|L_{\rm Vdd1-Gnd2}| + |L_{\rm Vdd2-Gnd1}| > |L_{\rm Vdd1-Vdd2}| + |L_{\rm Gnd1-Gnd2}|.$$

(9)

For fully interdigitated power distribution grids with DSDG, the distance between the power and ground lines inside each loop  $d_I^i$  is the same as an offset between the two loops  $s_I^i$ . In this case, substituting the mutual inductances between the power and ground paths in the two voltage domains into (8),  $M_{\text{loop}}^{\text{intI}}$  between the two grids is determined by (5). Observe that  $M_{\text{loop}}^{\text{intI}}$  is negative. A derivation of the mutual coupling between the two current loops in fully interdigitated power distribution grids with DSDG is provided in Appendix I.

Authorized licensed use limited to: Technion Israel School of Technology. Downloaded on April 12, 2009 at 11:11 from IEEE Xplore. Restrictions apply

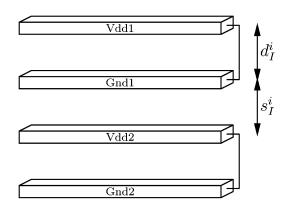

Fig. 6. Physical structure of a pseudo-interdigitated power distribution grid with DSDG. The distance between the lines making the loops  $d_{II}^i$  is two times greater than the separation between the lines.

### B. Type II Interdigitated Grids With DSDG

In the second type of interdigitated power distribution grids, a power/ground line from one voltage domain is placed next to a power/ground line from the other voltage domain. Groups of power/ground lines are alternated and equidistantly spaced, as shown in Fig. 6. Since one loop is located inside the other loop, the separation between the two loops  $s_{II}^i$  is negative. These power distribution grids are described here as *pseudo-interdigitated* power distribution grids with DSDG.

The mutual inductive coupling of two current loops in pseudo-interdigitated grids with DSDG is determined by (8). For pseudo-interdigitated power distribution grids with DSDG, the distance between the power and ground lines inside each loop  $d_{\rm II}^i$  is two time greater than the offset between the two loops  $s_{\rm II}^i$ . In this case, substituting the mutual inductance between the power and ground paths in the different voltage domains into (8), the mutual inductive coupling between the two networks  $M_{\rm loop}^{\rm intII}$  is

$$M_{\rm loop}^{\rm intII} = 0.2l \left( \ln 3 - \frac{2d}{l} \right) \tag{10}$$

where d is the distance between the two adjacent lines. Observe that  $M_{\text{loop}}^{\text{intII}}$  is positive for  $l \gg d$ . A derivation of the mutual coupling between the two current loops in pseudo-interdigitated power distribution grids with DSDG is presented in Appendix II.

In modern high-performance ICs, the inductive component of the power distribution noise has become comparable to the resistive noise [20]. In future nanoscale ICs, the inductive L di/dtvoltage drop will dominate the resistive IR voltage drop, becoming the major component in the overall power noise. The partial self-inductance of the metal lines comprising the power distribution grid is constant for fixed parameters of a power delivery system (i.e., the line width, line thickness, and line length). In order to reduce the power distribution noise, the total mutual inductance of a particular power distribution grid should therefore be negative with the maximum absolute value.

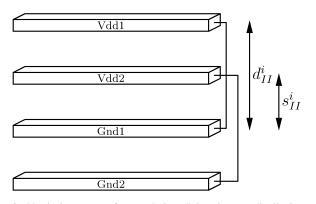

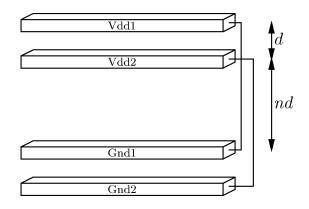

Comparing (5) to (10), note that for a line separation d much smaller than line length l, the mutual inductive coupling between different voltage domains in fully interdigitated grids  $M_{\text{loop}}^{\text{intI}}$  is negative with a nonzero absolute value, whereas the mutual inductive coupling between two current loops in

Fig. 7. Total mutual inductance of interdigitated power distribution grids with DSDG as a function of line separation. The length of the lines is  $1000 \,\mu$ m.

pseudo-interdigitated grids  $M_{\rm loop}^{\rm intII}$  is positive. Moreover, since the distance between the lines comprising the loop in fully interdigitated power distribution grids is two times smaller than the line separation inside each current loop in pseudo-interdigitated power distribution grids, the mutual inductance inside the loop  $M'_{\rm intI}$  is larger than  $M'_{\rm intII}$ . Thus, the total mutual inductance as described by (7) in fully interdigitated grids is further increased by  $M_{\rm loop}^{\rm intI}$ . Conversely, the total mutual inductance in pseudo-interdigitated grids is reduced by  $M_{\rm loop}^{\rm intII}$ , as shown in Fig. 7. The total mutual inductance in fully interdigitated power distribution grids with DSDG is therefore greater than the total mutual inductance in pseudo-interdigitated grids with DSDG.

### VI. PAIRED GRIDS WITH DSDG

Another type of power distribution grid with alternating power and grounds lines is paired power distribution grids [6], [21]. Similar to interdigitated grids, the power and ground lines in paired grids are alternated, but rather than placed equidistantly, the lines are placed in equidistantly spaced pairs of adjacent power and ground lines. Analogous to the concepts presented in Section IV, the loop inductance of a particular power distribution network in paired power distribution grids with DSDG is affected by the presence of the other power distribution network.

In general, multiple paired power distribution grids with DSDG can be designed to satisfy different design constraints in high-performance ICs. Exploiting the symmetry between the power and ground networks, each of the possible paired power distribution grids with DSDG can be characterized by the two main power delivery schemes. Two types of paired power distribution grids with DSDG are presented in this section. The loop inductance in the first type of power distribution grids is described in Section VI-A. The loop inductance in the second type of power distribution grids is discussed in Section VI-B.

### A. Type I Paired Grids With DSDG

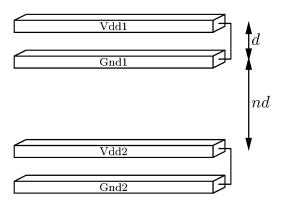

In the first type of paired power distribution grids with DSDG, the power and ground lines of a particular power delivery net-

Fig. 8. Physical structure of a fully paired power distribution grid with DSDG. In this grid structure, each pair is composed of power and ground lines for a particular voltage domain. The separation between the pairs is n times larger than the distance between the lines making up the loop d.

work are placed in equidistantly spaced pairs. The group of adjacent power and ground lines from one voltage domain is alternated with the group of power and ground lines from the other voltage domain, as shown in Fig. 8. In these power distribution grids, the power and ground lines from a specific power delivery network are placed in pairs. Such power distribution grids are described here as *fully paired* power distribution grids with DSDG. Note that in the case of n = 1, fully paired grids degenerate to fully interdigitated grids.

Similar to the mutual inductance between the two loops in interdigitated power distribution grids, as discussed in Section V, the mutual inductive coupling of the two current loops in fully paired grids with DSDG is determined by (8). In fully paired power distribution grids with DSDG, the distance between the pairs is *n* times greater than the separation *d* between the power and ground lines making up the pair. Thus, substituting the mutual inductance between the power and ground lines for the different voltage domains into (8), the mutual inductive coupling between the two networks  $M_{\text{loop}}^{\text{prdI}}$  is

$$M_{\rm loop}^{\rm prdI} = 0.2l \ln\left[\frac{(n+2)n}{(n+1)^2}\right].$$

(11)

A derivation of the mutual coupling between the two current loops in fully paired power distribution grids with DSDG is presented in Appendix III. Note that  $M_{\text{loop}}^{\text{prdI}}$  is negative for  $n \ge 1$  with an absolute value slightly greater than zero. Also note that the mutual inductance inside each current loop  $M'_{\text{prdI}}$  does not depend on n and is determined by (3).

### B. Type II Paired Grids With DSDG

In the second type of paired power distribution grids with DSDG, a power/ground line from one voltage domain is placed in a pair with a power/ground line from the other voltage domain. The group of adjacent power lines alternates with the group of ground lines from different voltage domains, as shown in Fig. 9. In these power distribution grids, the power and ground lines from different power delivery networks are placed in pairs. These power distribution grids are described here as *pseudopaired* power distribution grids with DSDG. Note that in the case of n = 1, pseudo-paired grids are identical to pseudo-interdigitated grids.

Fig. 9. Physical structure of a pseudo-paired power distribution grid with DSDG. In this grid structure, each pair is composed of power or ground lines from the two voltage domains. The separation between the pairs is n times larger than the distance between the lines making up the loop d. The effective distance between the power and ground lines in a particular power delivery network is (n + 1)d.

As discussed in Section VI-A, the mutual inductive coupling between the two power delivery networks in pseudo-paired grids with DSDG is determined by (8). In pseudo-paired power distribution grids with DSDG, the distance between the pairs is ntimes greater than the separation d between the power/ground lines making up the pair. The effective distance between the power and ground lines in a particular power delivery network is therefore (n + 1)d. Substituting the mutual inductances between the power and ground lines in the two different voltage domains into (8), the mutual inductive coupling between the two networks  $M_{\text{loop}}^{\text{prdII}}$  is

$$M_{\text{loop}}^{\text{prdII}} = 0.2l \left[ \ln(n^2 + 2n) - \frac{2nd}{l} \right].$$

(12)

A derivation of the mutual coupling between the two current loops in pseudo-paired power distribution grids with DSDG is provided in Appendix IV. Note that  $M_{\text{loop}}^{\text{prdII}}$  is positive for  $n \geq 1$ . In contrast to fully paired grids, in pseudo-paired power distribution grids, the mutual inductance inside each current loop  $M'_{\text{prdII}}$  is a function of n

$$M'_{\rm prdII} = 0.2l \left[ \ln \frac{2l}{(n+1)d} - 1 + \frac{(n+1)d}{l} - \ln \gamma + \ln k \right].$$

(13)

Note that  $M'_{\text{prdII}}$  decreases with *n*, approaching zero for large *n*.

Comparing Fig. 8 to Fig. 9, note that the line separation inside each pair in the pseudo-paired power distribution grids is *n* times greater than the line separation between the power and ground lines making up the pair in fully paired power distribution grids. The mutual inductance within the power delivery network in fully paired power distribution grids  $M'_{\rm prdI}$ is therefore greater than the mutual inductance within the power delivery network in pseudo-paired power distribution grids  $M'_{\rm prdII}$ . Moreover, the distance between the lines in the particular voltage domain in fully paired power distribution grids does not depend on the separation between the pairs (no dependence on *n*). Thus,  $M'_{\rm prdI}$  is a constant. The distance between the power/ground lines from the different voltage domains in pseudo-paired power distribution grids is smaller, however, than the distance between the power/ground lines from the different power delivery networks in fully paired power distribution grids. The magnitude of the mutual inductive coupling between the two current loops in pseudo-paired grids  $M_{\rm loop}^{\rm prdII}$  is therefore larger than the magnitude of the mutual inductive coupling between the two power delivery networks in fully paired grids  $M_{\rm loop}^{\rm prdII}$ . Note that the magnitude of  $M_{\rm loop}^{\rm prdII}$  increases with n and becomes much greater than zero for large n. Also note that  $M_{\rm loop}^{\rm prdII}$  is negative while  $M_{\rm loop}^{\rm prdII}$  is positive for all  $n \geq 1$ .

The total mutual inductance M as determined by (7) for two types of paired power distribution grids with DSDG is plotted in Fig. 10. Note that the total mutual inductance in fully paired grids is primarily determined by the mutual inductance inside each power delivery network  $M'_{\rm prdI}$ . The absolute value of the total mutual inductance in fully paired grids is further increased by  $M_{\text{loop}}^{\text{prdI}}$ . As the separation between the pairs n increases, the mutual inductive coupling between the two current loops  $M_{

m loop}^{

m prdI}$ decreases, approaching zero at large n. Thus, the magnitude of the total mutual inductance in fully paired power distribution grids slightly drops with n. In pseudo-paired grids, however, the total mutual inductance is a non-monotonic function of n and can be divided into two regions. The total mutual inductance is determined by the mutual inductance inside each current loop  $M'_{\text{prdII}}$  for small n and by the mutual inductive coupling between the two voltage domains  $M_{\text{loop}}^{\text{prdII}}$  for large n. Since  $M'_{\text{prdII}}$  is negative and  $M_{\text{loop}}^{\text{prdII}}$  is positive for all n, the total mutual inductance in pseudo-paired grids is negative with a decreasing absolute value for small n. As n increases,  $M_{\text{loop}}^{\text{prdII}}$ begins to dominate and, at some n (n = 8 in Fig. 10), the total mutual inductance becomes positive with increasing absolute value. For large n, pseudo-paired grids with DSDG become identical to power distribution grids with DSSG. Similar to grids with DSSG, power and ground paths in both voltage domains are strongly coupled, increasing the loop inductance as seen from a specific power delivery network. The resulting voltage fluctuations are therefore larger.

### VII. SIMULATION RESULTS

To characterize the voltage fluctuations as seen at the load, both power distribution grids are modeled as ten series RL segments. It is assumed that both power delivery subnetworks are similar and source similar current loads. Two equal current loads are applied to the power grid with a single supply voltage and single ground (SSSG). A triangular current source (50-mA amplitude, 100-ps rise time, and 150-ps fall time) is applied to each grid within the power distribution network. No skew between the two current loads is assumed, modeling the worst case scenario with the maximum power noise. For each grid structure, the width of the lines varies from 1  $\mu$ m to 10  $\mu$ m, maintaining the line pair pitch P at a constant value of 40  $\mu$ m (80  $\mu$ m in the case of paired grids). In paired power distribution grids, the line separation inside each pair is 1  $\mu$ m. The decrease in the maximum voltage drop (or the voltage sag) from  $V_{dd}$  is estimated from SPICE for different line widths.

Note that in the case of DSSG, only interdigitated grids can be implemented. The power grids with DSSG lack symmetry in

Fig. 10. Total mutual inductance of paired power distribution grids with DSDG as a function of the ratio of the distance between the pairs to the line separation inside each pair, n. The length of the lines is 1000  $\mu$ m and the line separation inside each pair d is 1  $\mu$ m. Note that the total mutual inductance in pseudo-paired power distribution grids becomes zero at n = 8.

both voltage domains which is necessary for paired grids. Also note that two types of interdigitated power distribution grids with DSSG can be implemented. Both types of interdigitated grids with DSSG are identical except for those power/ground lines located at the periphery of the power grid. Thus, the difference in loop inductance in both interdigitated grids with DSSG is negligible for a large number of power/ground lines comprising the grid. Only one interdigitated power distribution grid with DSSG is therefore analyzed.

The performance of interdigitated power distribution grids is quantitatively compared to the power noise of a conventional power distribution scheme with DSSG in Section VII-A. The maximum voltage drop from  $V_{dd}$  for paired power distribution grids is evaluated in Section VII-B. Both types of power distribution grids are compared to the reference power distribution grid with SSSG. Power distribution schemes with decoupling capacitors are compared in Section VII-C. The dependence of the power noise on the switching frequency of the current loads is discussed in Section VII-D.

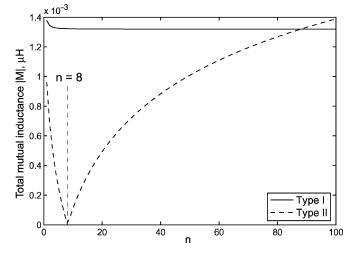

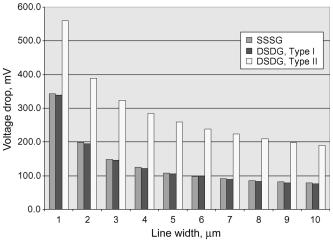

# A. Interdigitated Power Distribution Grids Without Decoupling Capacitors

The maximum voltage drop for four interdigitated power distribution grids without decoupling capacitors is depicted in Fig. 11. For each of the power distribution grids, the maximum voltage drop decreases sublinearly as the width of the lines is increased. This noise voltage drop is caused by the decreased loop impedance. The resistance of the metal lines decreases linearly with an increase in the line width. The loop inductance increases slowly with increasing line width. As a result, the total impedance of each of the power distribution schemes decreases sublinearly, approaching a constant impedance as the lines become very wide.

As described in Section IV, the power distribution scheme with DSDG outperforms power distribution grids with DSSG. Fully interdigitated grids with DSDG produce, on average, a 15.3% lower voltage drop as compared to the scheme with

Fig. 11. Maximum voltage drop for the four interdigitated power distribution grids under investigation. No decoupling capacitors are added.

DSSG. Pseudo-interdigitated grids with DSDG produce, on average, a close to negligible 0.3% lower voltage drop as compared to the scheme with DSSG. The maximum improvement in noise reduction is 16.5%, which is achieved for an 8- $\mu$ m-wide line, and 7.1%, which is achieved for a 1- $\mu$ m-wide line, for fully and pseudo-interdigitated grids with DSDG, respectively. Note that pseudo-interdigitated power grids with DSDG outperform conventional power delivery schemes with DSSG for narrow lines. For wide lines, however, the power delivery scheme with DSSG results in a lower voltage drop. From the results depicted in Fig. 11, observe that the power delivery schemes with both DSDG and SSSG outperform the power grid with DSSG. The fully interdigitated power distribution grid with DSDG outperforms the reference power grid with SSSG by 2.7%. This behavior can be explained as follows. Since the number of lines dedicated to each power delivery network in the grid with DSDG is two times smaller than the total number of lines in the reference grid, the resistance of each subnetwork is two times greater than the resistance of the reference power grid. The loop inductance of an interdigitated power distribution grid depends inversely linearly on the number of lines in the grid [21]. The loop inductance of each subnetwork is two times greater than the overall loop inductance of the grid with SSSG. Given two similar current loads applied to the reference power distribution scheme, the maximum voltage drop for both systems should be the same. However, from (4), the mutual inductive coupling in the power grid with DSDG increases due to the presence of the second subnetwork. As a result, the overall loop inductance of each network comprising the power grid with DSDG is lower, resulting in a lower power noise as seen from the current load of each subnetwork. Note from Fig. 7 that in pseudo-interdigitated power distribution grids with DSDG, the mutual inductance between two current loops  $M_{

m loop}^{

m intII}$  is positive, reducing the overall mutual inductance. The resulting loop inductance as seen from the load of the particular network is therefore increased, producing a larger inductive voltage drop. In many applications such as high-performance microprocessors, mixed-signal circuits, and systems-on-chip, a power distribution network with DSDG is often utilized. In

Fig. 12. Maximum voltage drop for the three paired power distribution grids under investigation. No decoupling capacitors are added.

other applications, however, a fully interdigitated power distribution system with multiple voltages and multiple grounds can be a better alternative than distributing power with SSSG.

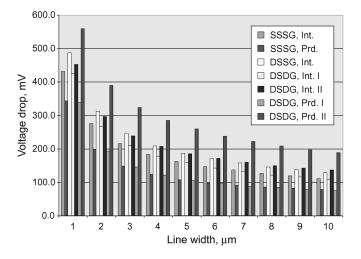

# *B. Paired Power Distribution Grids Without Decoupling Capacitors*

The maximum voltage drop for three paired power distribution grids without decoupling capacitors is depicted in Fig. 12. Similar to interdigitated grids, the maximum voltage drop decreases sublinearly with increasing line width. Observe that fully paired power distribution grids with DSDG outperform conventional paired power distribution grids with SSSG by, on average, 2.3%. Note the information shown in Fig. 12. The ratio of the separation between the pairs to the distance between the lines in each pair (n) is 80. Also note from Fig. 10 that the total mutual inductance in fully paired grids increases as n is decreased (the pairs are placed physically closer). Thus, higher performance is achieved in fully paired grids with DSDG for densely placed pairs. In contrast to fully paired grids, in pseudo-paired grids with DSDG, the total mutual inductance is reduced by inductive coupling between the two current loops  $M_{\text{loop}}^{\text{prdII}}$ . For n > 8 (see Fig. 10), the mutual inductive coupling between the two current loops in a pseudo-paired grid becomes comparable to the mutual inductive coupling between the two current loops in the conventional power grid with DSSG (the -2M term in (2) becomes positive). As *n* further increases, the power and ground paths within the two voltage domains become strongly coupled, increasing the loop inductance.

To quantitatively compare interdigitated grids to paired grids, the maximum voltage drop for seven different types of power distribution grids without decoupling capacitors is plotted in Fig. 13. Note in Fig. 13 that the conventional power delivery scheme with DSSG results in larger voltage fluctuations as compared to fully interdigitated grids with DSDG. The performance of pseudo-interdigitated grids with DSDG is comparable to the performance of a conventional delivery scheme with DSSG. In pseudo-interdigitated grids, the positive mutual inductance between two current loops lowers the overall negative mutual inductance. The loop inductance in the specific power delivery

Fig. 13. Maximum voltage drop for interdigitated and paired power distribution grids under investigation. No decoupling capacitors are added.

network is therefore increased, resulting in greater power noise. Analogous to the conventional scheme, in pseudo-paired grids, the power and ground paths in different voltage domains are strongly coupled, producing the largest voltage drop. Both fully interdigitated and fully paired power distribution grids with DSDG produce the lowest voltage fluctuations, slightly outperforming the reference power delivery network with SSSG. In these grids, the resulting loop inductance is reduced due to strong coupling between the power/ground pairs from different voltage domains (with currents flowing in opposite directions). Alternatively, the total mutual inductance is negative with a large magnitude, reducing the loop inductance. Both fully interdigitated and fully paired power distribution grids with DSDG should be used in those systems with multiple power supply voltages. Fully interdigitated and fully paired power distribution grids with DSDG can also be a better alternative than a power distribution grid with SSSG.

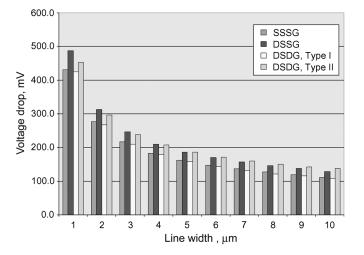

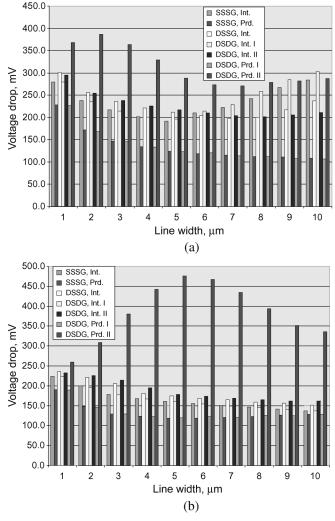

### C. Power Distribution Grids With Decoupling Capacitors

To lower the voltage fluctuations of on-chip power delivery systems, decoupling capacitors are placed on ICs to provide charge when the voltage drops [6]. The maximum voltage drop of seven power distribution schemes with decoupling capacitors operating at 1 GHz is shown in Fig. 14. All of the decoupling capacitors are assumed to be ideal, i.e., no parasitic resistances and inductances are associated with the capacitor. Also, all of the decoupling capacitors are assumed to be useful (located inside the effective radius of an on-chip decoupling capacitor [22], [23]). The total budgeted capacitance is divided equally between the two supply voltages. The decoupling capacitor added to the power distribution grid with SSSG is two times larger than the decoupling capacitor in each subnetwork of the power delivery scheme with dual voltages. As shown in Fig. 14, the maximum voltage drop decreases as the lines become wider. The maximum voltage drop of the proposed fully interdigitated power distribution scheme with DSDG is reduced by, on average, 9.2% (13.6% maximum) for a 30-pF decoupling capacitance as compared to a conventional power distribution scheme with DSSG.

Fig. 14. Maximum voltage drop for seven types of power distribution grids with a decoupling capacitance of (a) 20 pF and (b) 30 pF added to each power supply. The switching frequency of the current loads is 1 GHz.

For a 20-pF decoupling capacitance, however, a fully interdigitated power distribution grid with DSDG produces about 55% larger power noise as compared to a conventional power distribution scheme with DSSG. This performance degradation is caused by on-chip resonances, as explained below.

Comparing the data shown in Fig. 13 to that shown in Fig. 14, note that the voltage drop of the power distribution grids with decoupling capacitors as compared to the case with no decoupling capacitances is greatly reduced for narrow lines and is higher for wider lines. This behavior can be explained as follows. For narrow lines, the grid resistance is high and the loop inductance is low. The grid impedance, therefore, is primarily determined by the resistance of the lines. Initially, the system with an added decoupling capacitor is overdamped. As the lines become wider, the grid resistance decreases faster than the increase in the loop inductance and the system becomes less damped. As the loop inductance increases, the resonant frequency of an RLC circuit, formed by the on-chip decoupling capacitor and the parasitic RL impedance of the grid, decreases. This resonant frequency moves closer to the switching frequency of the current load. As a result, the voltage response of the overall system oscillates. Since the decoupling capacitance added to the power grid with SSSG is two times larger than the decoupling capacitance added to each power supply voltage in the dual voltage schemes, the system with a single supply voltage is more highly damped and the self-resonant frequency is significantly lower. Furthermore, the resonant frequency is located far from the switching frequency of the circuit.

For narrow lines propagating a signal with 1-GHz harmonics, the resulting power noise in fully interdigitated power grids with DSDG with 20 pF added on-chip decoupling capacitance is smaller than the power noise of the power distribution scheme with SSSG, as shown in Fig. 14(a). With increasing line width, the inductance of the power grids increases more slowly than the decrease in the grid resistance. An *RLC* system formed by the RL impedance of the power grid and the decoupling capacitance, therefore, is less damped. Both of the power distribution grids with DSDG and the conventional power distribution grid with SSSG result in larger voltage fluctuations as the line width increases. The self-resonant frequency of the fully interdigitated grid with DSDG is almost coincident with the switching frequency of the current load. The self-resonant frequency of the power grid with SSSG however is different from the switching frequency of the current source. Thus, for wide lines, a conventional power delivery scheme with SSSG outperforms the proposed fully interdigitated power distribution grid with DSDG. Note that the loop inductance in pseudo-interdigitated power distribution grids with DSDG is greater than the loop inductance in fully interdigitated grids. As a result, the self-resonant frequency of the pseudo-interdigitated grid with DSDG is smaller than the switching frequency of the current load, resulting in a smaller power noise as compared to power grids with SSSG and fully interdigitated grids with DSDG. Also note that the loop inductance in paired power distribution grids is further reduced as compared to interdigitated grids. In this case, the self-resonant frequency of all of the paired power distribution grids is greater than the circuit switching frequency. Thus, the power noise in paired power distribution grids gradually decreases as the line width increases (and is slightly higher in wide lines in the case of pseudo-paired grids).

Increasing the on-chip decoupling capacitance from 20 to 30 pF further reduces the voltage drop. For a 30-pF decoupling capacitance in a pseudo-paired power delivery scheme with DSSG, the self-resonant frequency is close to the switching frequency of the current load. Simultaneously, the grid resistance decreases much faster with increasing line width than the increase in the loop inductance. The system becomes underdamped with the self-resonant frequency equal to the circuit switching frequency. As a result, the system produces high-amplitude voltage fluctuations. The maximum voltage drop in the case of a pseudo-paired power grid with DSDG therefore increases as the lines become wider. This phenomenon is illustrated in Fig. 14(b) for a line width of 5  $\mu$ m.

With decoupling capacitors, the self-resonant frequency of an on-chip power distribution system is lowered. If the resonant frequency of an RLC system with intentionally added decoupling capacitors is sufficiently close to the circuit switching frequency, the system will produce high-amplitude voltage fluc-

Fig. 15. Maximum voltage drop for the power distribution grid with SSSG as a function of frequency and line width for different values of decoupling capacitance: (a) decoupling capacitance budget of 20 pF; (b) decoupling capacitance budget of 30 pF.

tuations. Voltage sagging will degrade system performance and may cause significant failure. An excessively high power supply voltage can degrade the reliability of a system. The system of decoupling capacitors for power distribution networks with multiple supply voltages therefore has to be carefully designed. Improper choice (magnitude and location) of the on-chip decoupling capacitors can worsen the power noise, further degrading system performance [15], [16], [22], [23].

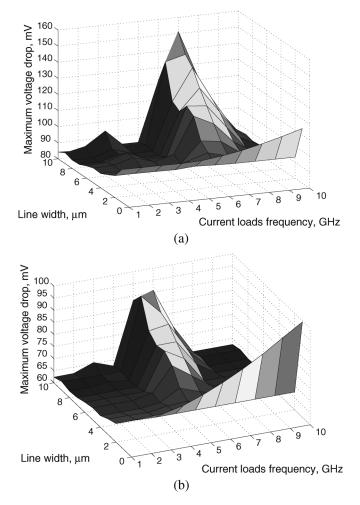

### D. Dependence of Power Noise on the Switching Frequency of the Current Loads

To model the dependence of the power noise on the switching frequency, the power grids are stimulated with triangular current sources with a 50-mA amplitude, 20-ps rise times, and 30-ps fall times. The switching frequency of each current source varies from 1 to 10 GHz to capture the resonances in each power grid. For each grid structure, the width of the line is varied from 1  $\mu$ m to 10  $\mu$ m. The maximum voltage drop is determined from SPICE for different line widths at each frequency.

The maximum voltage drop for the power distribution grid with SSSG is illustrated in Fig. 15. The maximum voltage drop decreases slightly for wider lines. Note that with decoupling capacitors, the voltage drop is lower except for two regions. The significant increase in power noise at specific frequencies and line widths is due to the following two effects. As lines become wider, the resistance of the power grid is lowered, whereas the inductance is slightly increased, decreasing the damping of the entire system. When the switching frequency of a current load approaches the self-resonant frequency of the power grid, the voltage drop due to the *RLC* system increases (due to resonances). As the width of the lines increases, the system becomes more underdamped, resulting in a sharper resonant peak. The amplitude of the resonant peak increases rapidly as the system becomes less damped. The maximum voltage drop occurs between 6 and 7 GHz for a power grid with a 20-pF decoupling capacitance, as shown in Fig. 15(a).

The maximum voltage drop also increases at high frequencies in narrow lines. Decoupling capacitors are effective only if the capacitor is fully charged within one clock cycle. The effectiveness of the decoupling capacitor is related to the RCtime constant, where R is the resistance of the interconnect connecting the capacitor to the power supply. For narrow resistive lines, the time constant is prohibitively large at high frequencies, i.e, the decoupling capacitor cannot be fully charged within one clock period. The effective magnitude of the decoupling capacitor is therefore reduced. The capacitor has the same effect on the power noise as a smaller capacitor [22], [23].

By increasing the magnitude of the decoupling capacitor, the overall power noise can be further reduced, as shown in Fig. 15(b). Moreover, the system becomes more damped, producing a resonant peak with a smaller amplitude. The self-resonant frequency of the power delivery system is also lowered. Comparing Fig. 15(a) to (b), note that the resonant peak shifts in frequency from approximately 6-7 GHz for a 20-pF decoupling capacitance to 5-6 GHz for a 30-pF decoupling capacitance. Concurrently, increasing the decoupling capacitor increases the RC time constant, making the capacitor less effective at high frequencies in narrow resistive lines. Note the significant increase in the maximum voltage drop for a 1- $\mu$ m-wide line for a 30-pF decoupling capacitance as compared to the case of a 20-pF decoupling capacitance. Power distribution grids with DSSG and DSDG behave similarly. For the same decoupling capacitance and for the nonresonant case, both the fully and pseudo-interdigitated power distribution schemes with DSDG result in a lower voltage drop than a power distribution scheme with DSSG. The magnitude of the decoupling capacitance needs to be carefully chosen to guarantee that the two prohibited regions are outside the operating frequency of the system for a particular line width. Also, for narrow lines, the magnitude of the decoupling capacitor is limited by the RC time constant. The amplitude of the resonant peak can be lowered by increasing the parasitic resistance of the decoupling capacitors.

### VIII. DESIGN IMPLICATIONS

Historically, due to low switching frequencies and the high resistance of on-chip interconnects, resistive voltage drops have dominated the overall power noise. In modern high-performance ICs, the inductive component of the power distribution noise has become comparable to the resistive noise [6]. It is expected that in future nanoscale ICs, the inductive L(di/di) voltage drop will dominate the resistive IR voltage drop, becoming the primary component of the overall power noise [20]. As shown previously, the performance of the proposed power delivery schemes with DSDG depends upon the switching frequency of the current load, improving with frequency (due to increased mutual coupling between the power and ground lines). It is expected that the performance of the proposed power distribution grids with DSDG will increase in the future.

As discussed in Section VII, fully interdigitated power distribution grids with DSDG outperform pseudo-interdigitated grids with DSDG. Moreover, in pseudo-interdigitated grids, the power/ground lines from different voltage domains are placed next to each over, increasing the coupling between the different power supply voltages. Pseudo-interdigitated power distribution grids with DSDG should therefore not be used in those ICs where high isolation is required between the power supply voltages (e.g., mixed-signal ICs, systems-on-chip). Rather, fully interdigitated power distribution grids with DSDG should be utilized.

Similar to interdigitated grids, fully paired power distribution grids with DSDG produce smaller power noise as compared to pseudo-paired power distribution grids with DSDG. In pseudo-paired grids, the separation between the power/ground lines from different voltage domains is much smaller than the distance between the power and ground lines inside each power delivery network (current loop). Different power supply voltages are therefore strongly coupled in pseudo-paired grids. Note that pseudo-paired grids have the greatest coupling between different power supplies among all of the power distribution schemes described in this paper. Such grids, therefore, are not a good choice for distributing power in mixed-signal ICs. Later in the design flow, when it is prohibitively expensive to redesign the power distribution system, the spacing between the pairs in pseudo-paired grids with DSDG should be decreased. If the pairs are placed close to each over (n is small), as illustrated in Fig. 10, the loop inductance of a particular current loop is lowered, approaching the loop inductance in pseudo-interdigitated grids.

The self-resonant frequency of a system is determined by the power distribution network. For example, in power distribution grids with DSDG, the decoupling capacitance added to each power delivery network is two times smaller than the decoupling capacitance in the power delivery scheme with SSSG. The loop inductance of power distribution grids with DSDG is comparable however to the loop inductance of power distribution grids with SSSG. Assuming the same decoupling capacitance, the self-resonant frequency of power distribution grids with DSDG is higher than the self-resonant frequency of the reference power delivery scheme with SSSG, increasing the maximum operating frequency of the overall system. Note that for comparable resonant frequencies, the resistance of the power distribution grid with DSDG is two times greater than the resistance of a conventional power grid with SSSG. Thus, power distribution grids with DSDG are more highly damped, resulting in reduced voltage fluctuations at the resonant frequency.

### IX. CONCLUSION

Power distribution grids with multiple power supply voltages are analyzed in this paper. Two types of interdigitated and paired on-chip power distribution grids with DSDG are proposed. Closed form expressions to estimate the loop inductance in four types of power distribution grids with DSDG have been developed. With no decoupling capacitors placed between the power supply and ground, the proposed fully and pseudo-interdigitated power distribution grids outperform a conventional interdigitated power distribution grid with DSSG by 15.3% and 0.3%, respectively, in terms of lower power noise. In the case of power grids with decoupling capacitors, the voltage drop is reduced by about 9.2% for fully interdigitated grids with a 30-pF additional decoupling capacitance and is higher by 55.4% in the case of a 20-pF added decoupling capacitance. This degradation in performance in fully interdigitated grids with DSDG is caused by voltage oscillations at the resonant frequency.

The performance of the proposed on-chip power distribution grids is compared to a reference power distribution grid with SSSG. If no decoupling capacitors are added, the voltage drop of a fully interdigitated power distribution grid with DSDG is reduced by, on average, 2.7% as compared to the voltage drop of an interdigitated power distribution grid with SSSG. In the case of the fully paired grid, the resulting power noise is reduced by about 2.3% as compared to the reference paired power distribution grid with SSSG. With on-chip decoupling capacitors added to the power delivery networks, both fully interdigitated and fully paired power distribution grids with DSDG slightly outperform the reference power distribution scheme with SSSG. On-chip decoupling capacitors are shown to lower the self-resonant frequency of the on-chip power distribution grid, producing resonances. The system of on-chip decoupling capacitors in power distribution systems with multiple supply voltages therefore requires careful design. Improper choice of the on-chip decoupling capacitors can degrade the performance of a system. It is noted that fully interdigitated and fully paired power distribution grids with DSDG should be utilized in those ICs where high isolation is required between the power supply voltages so as to effectively decouple the power supplies.

### Appendix I

# MUTUAL LOOP INDUCTANCE IN FULLY INTERDIGITATED POWER DISTRIBUTION GRIDS WITH DSDG

Assuming  $d_I^i = s_I^i = d$  and substituting the mutual inductance between the power and ground paths of the different voltage domains into (8), the mutual inductive coupling  $M_{\text{loop}}^{\text{intI}}$ between the two current loops in a fully interdigitated power distribution grid with DSDG is

$$M_{\text{loop}}^{\text{intI}} = 0.2l \left( \ln \frac{2l}{2d} - 1 + \frac{2d}{l} - \ln \gamma + \ln k - \ln \frac{2l}{3d} + 1 - \frac{3d}{l} + \ln \gamma - \ln k + \ln \frac{2l}{2d} - 1 + \frac{2d}{l} - \ln \gamma + \ln k - \ln \frac{2l}{d} + 1 - \frac{d}{l} + \ln \gamma - \ln k \right).$$

(14)

Simplifying (14) and considering that  $\ln \gamma$  and  $\ln k$  are approximately the same for different distances between the lines,  $M_{\text{loop}}^{\text{intI}}$  is

$$M_{\text{hoop}}^{\text{intI}} = 0.2l \left( \ln \frac{2l}{2d} - \ln \frac{2l}{3d} + \ln \frac{2l}{2d} - \ln \frac{2l}{d} \right)$$

=  $0.2l \ln \frac{2l \times 3d \times 2l \times d}{2d \times 2l \times 2d \times 2l} = 0.2l \ln \frac{3}{4} < 0.$  (15)

### Appendix II Mutual Loop Inductance in Pseudo-Interdigitated Power Distribution Grids With DSDG

Assuming  $d_{\rm II}^i = 2d$  and  $s_{\rm II}^i = d$  and substituting the mutual inductance between the power and ground paths of the different voltage domains into (8), the mutual inductive coupling  $M_{\rm loop}^{\rm intII}$  between the two current loops in a pseudo-interdigitated power distribution grid with DSDG is

$$M_{\text{loop}}^{\text{intII}} = 0.2l \left( \ln \frac{2l}{d} - 1 + \frac{d}{l} - \ln \gamma + \ln k - \ln \frac{2l}{3d} + 1 - \frac{3d}{l} + \ln \gamma - \ln k + \ln \frac{2l}{d} - 1 + \frac{d}{l} - \ln \gamma + \ln k - \ln \frac{2l}{d} + 1 - \frac{d}{l} + \ln \gamma - \ln k \right).$$

(16)

Simplifying (16) and considering that  $\ln \gamma$  and  $\ln k$  are approximately the same for different distances between the lines,  $M_{\text{loop}}^{\text{intII}}$  is

$$M_{\text{loop}}^{\text{intII}} = 0.2l \left( \ln \frac{2l}{d} - \ln \frac{2l}{3d} + \ln \frac{2l}{d} - \ln \frac{2l}{d} - \frac{2d}{l} \right)$$

$$= 0.2l \left( \ln \frac{2l \times 3d \times 2l \times d}{d \times 2l \times d \times 2l} - \frac{2d}{l} \right)$$

$$= 0.2l \left( \ln 3 - \frac{2d}{l} \right) > 0.$$

(17)

# APPENDIX III MUTUAL LOOP INDUCTANCE IN FULLY PAIRED POWER DISTRIBUTION GRIDS WITH DSDG

Assuming the separation between the pairs is n times larger than the distance between the power and ground lines inside each pair d (see Fig. 8) and substituting the mutual inductance between the power and ground paths of the different voltage domains into (8), the mutual inductive coupling  $M_{\text{loop}}^{\text{prdI}}$  between the two current loops in a fully paired power distribution grid with DSDG is

$$M_{\text{loop}}^{\text{prdI}} = 0.2l \left[ \ln \frac{2l}{(n+1)d} - 1 + \frac{(n+1)d}{l} - \ln \gamma + \ln k - \ln \frac{2l}{(n+2)d} + 1 - \frac{(n+2)d}{l} + \ln \gamma - \ln k + \ln \frac{2l}{(n+1)d} - 1 + \frac{(n+1)d}{l} - \ln \gamma + \ln k - \ln \frac{2l}{nd} + 1 - \frac{nd}{l} + \ln \gamma - \ln k \right].$$

(18)

Simplifying (18) and considering that  $\ln \gamma$  and  $\ln k$  are approximately the same for different distances between the lines,  $M_{\text{loop}}^{\text{prdI}}$  is

$$M_{\text{loop}}^{\text{prdI}} = 0.2l \left[ \ln \frac{2l}{(n+1)d} + \frac{(n+1)d}{l} - \ln \frac{2l}{(n+2)d} - \frac{(n+2)d}{l} + \ln \frac{2l}{(n+1)d} + \frac{(n+1)d}{l} - \ln \frac{2l}{nd} - \frac{nd}{l} \right]$$

$$= 0.2l \left[ \ln \frac{2l \times (n+2)d \times 2l \times nd}{(n+1)d \times 2l} + \frac{(n+1)d - (n+2)d + (n+1)d - nd}{l} \right]$$

$$= 0.2l \ln \left[ \frac{(n+2)n}{(n+1)^2} \right] < 0 \text{ for } n \ge 1.$$

(19)

# APPENDIX IV MUTUAL LOOP INDUCTANCE IN PSEUDO-PAIRED POWER DISTRIBUTION GRIDS WITH DSDG

Observing that the effective distance between the power and ground lines in a specific power delivery network is n + 1 times greater than the separation d between the lines making up the pair (see Fig. 9) and substituting the mutual inductance between the power and ground paths of the different voltage domains into (8), the mutual inductive coupling  $M_{\text{loop}}^{\text{prdII}}$  between the two current loops in a pseudo-paired power distribution grid with DSDG is

$$M_{\text{loop}}^{\text{prdII}} = 0.2l \left[ \ln \frac{2l}{d} - 1 + \frac{d}{l} - \ln \gamma + \ln k - \ln \frac{2l}{(n+2)d} + 1 - \frac{(n+2)d}{l} + \ln \gamma - \ln k + \ln \frac{2l}{d} - 1 + \frac{d}{l} - \ln \gamma + \ln k - \ln \frac{2l}{nd} + 1 - \frac{nd}{l} + \ln \gamma - \ln k \right].$$

(20)

Simplifying (20) and considering that  $\ln \gamma$  and  $\ln k$  are approximately the same for different distances between the lines,  $M_{\text{loop}}^{\text{prdII}}$  is

$$M_{\text{loop}}^{\text{prdII}} = 0.2l \left[ \ln \frac{2l}{d} + \frac{d}{l} - \ln \frac{2l}{(n+2)d} - \frac{(n+2)d}{l} + \ln \frac{2l}{d} + \frac{d}{l} - \ln \frac{2l}{nd} - \frac{nd}{l} \right]$$

=  $0.2l \left[ \ln \frac{2l \times (n+2)d \times 2l \times nd}{d \times 2l \times d \times 2l} + \frac{2d - (n+2)d - nd}{l} \right]$

=  $0.2l \left[ \ln(n^2 + 2n) - \frac{2nd}{l} \right] > 0 \text{ for } n \ge 1.$  (21)

### REFERENCES

Int. Technology Roadmap for Semiconductors, 2006 Update. Semiconductor Industry Association, ITRS, 2006.

- [2] K. Usami and M. Horowitz, "Clustered voltage scaling technique for low-power design," in *Proc. IEEE Int. Workshop Low Power Design*, Apr. 1995, pp. 3–8.

- [3] J.-M. Chang and M. Pedram, "Energy minimization using multiple supply voltages," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 5, no. 4, pp. 425–435, Dec. 1997.

- [4] S. Raje and M. Sarrafzadeh, "Variable voltage scheduling," in Proc. ACM Int. Symp. Low Power Design, Apr. 1995, pp. 9–14.

- [5] V. Kursun and E. G. Friedman, *Multi-Voltage CMOS Circuit Design*. New York: Wiley, 2006.

- [6] M. Popovich, A. V. Mezhiba, and E. G. Friedman, Power Distribution Networks With On-Chip Decoupling Capacitors. New York: Springer, 2008.

- [7] A. V. Mezhiba and E. G. Friedman, "Impedance characteristics of power distribution grids in nanoscale integrated circuits," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 12, no. 11, pp. 1148–1155, Nov. 2004.

- [8] W. S. Song and L. A. Glasser, "Power distribution techniques for VLSI circuits," *IEEE J. Solid-State Circuits*, vol. SSC-21, no. 1, pp. 150–156, Feb. 1986.

- [9] D. A. Priore, "Inductance on silicon for sub-micron CMOS VLSI," in Proc. IEEE Symp. VLSI Circuits, May 1993, pp. 17–18.

- [10] L.-R. Zheng and H. Tenhunen, "Effective power and ground distribution scheme for deep submicron high speed VLSI circuits," in *Proc. IEEE Int. Symp. Circuits Syst. (ISCAS)*, May 1999, vol. I, pp. 537–540.

- [11] M. Igarashi et al., "A Low-Power Design Method Using Multiple Supply Voltages," in Proc. IEEE Int. Symp. Low Power Electron. Design (ISLPED), Aug. 1997, pp. 36–41.

- [12] J.-S. Wang, S.-J. Shieh, J.-C. Wang, and C.-W. Yeh, "Design of standard cells used in low-power ASIC's exploiting the multiple-supply-voltage scheme," in *Proc. IEEE Int. ASIC Conf.*, Sep. 1998, pp. 119–123.

- [13] K. Usami *et al.*, "Automated low-power technique exploiting multiple supply voltages applied to a media processor," *IEEE J. Solid-State Circuits*, vol. 33, no. 3, pp. 463–472, Mar. 1998.

- [14] M. Kamon, M. J. Tsuk, and J. White, "FastHenry: A multipole-accelerated 3-D inductance extraction program," *IEEE Trans. Microw. Theory Tech.*, vol. 24, no. 9, pp. 1750–1758, Sep. 1994.

- [15] M. Popovich and E. G. Friedman, "Decoupling capacitors for power distribution systems with multiple power supply voltages," in *Proc. IEEE SOC Conf.*, Sep. 2004, pp. 331–334.

- [16] M. Popovich and E. G. Friedman, "Decoupling capacitors for multivoltage power distribution systems," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 14, no. 3, pp. 217–228, Mar. 2006.

- [17] E. B. Rosa, "The self and mutual inductance of linear conductors," Bulletin of the National Bureau of Standards, Government Printing Office, Washington, DC, Technical Paper Reprint No. 80, Jan. 1908, vol. 4(2), pp. 301–344.

- [18] A. V. Mezhiba and E. G. Friedman, "Properties of on-chip inductive current loops," in *Proc. ACM Great Lakes Symp. VLSI*, Apr. 2002, pp. 12–17.

- [19] M. Popovich, E. G. Friedman, M. Sotman, and A. Kolodny, "On-chip power distribution grids with multiple supply voltages for high performance integrated circuits," in *Proc. ACM Great Lake Symp. VLSI*, Apr. 2005, pp. 2–7.

- [20] A. V. Mezhiba and E. G. Friedman, "Scaling trends of on-chip power distribution noise," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 12, no. 4, pp. 386–394, Apr. 2004.

- [21] A. V. Mezhiba and E. G. Friedman, "Inductive properties of high performance power distribution grids," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 10, no. 6, pp. 762–776, Dec. 2002.

- [22] M. Popovich, E. G. Friedman, M. Sotman, A. Kolodny, and R. M. Secareanu, "Maximum effective distance of on-chip decoupling capacitors in power distribution grids," in *Proc. ACM/IEEE Great Lake Symp. VLSI*, Mar. 2006, pp. 173–179.

- [23] M. Popovich, M. Sotman, A. Kolodny, and E. G. Friedman, "Effective radii of on-chip decoupling capacitors," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, to be published.

**Mikhail Popovich** (M'08) received the B.S. degree in electrical engineering from Izhevsk State Technical University, Izhevsk, Russia, in 1998, and the M.S. and Ph.D. degrees in electrical and computer engineering from the University of Rochester, Rochester, NY, in 2002 and 2007, respectively.

He was an intern at Freescale Semiconductor, Inc., Tempe, AZ, in summer 2005, where he worked on signal integrity in RF and mixed-signal ICs and developed design techniques for placing distributed on-chip decoupling capacitors. In 2007, he joined Qualcomm Corporation, San Diego, CA, as a Senior Engineer. His research interests are in the areas of noise, signal integrity, and interconnect design including on-chip inductive effects, optimization of power distribution networks, and the design of on-chip decoupling capacitors.

Dr. Popovich received the Best Student Paper Award at the ACM Great Lakes Symposium on VLSI in 2005 and the GRC Inventor Recognition Award from the Semiconductor Research Corporation in 2007.

**Eby G. Friedman** (S'78–M'79–SM'90–F'00) received the B.S. degree from Lafayette College, Easton, PA, in 1979, and the M.S. and Ph.D. degrees from the University of California at Irvine in 1981 and 1989, respectively, all in electrical engineering.

From 1979 to 1991, he was with Hughes Aircraft Company, rising to the position of Manager of the Signal Processing Design and Test Department, responsible for the design and test of high-performance digital and analog ICs. He has been with the Department of Electrical and Computer Engineering at the

University of Rochester, Rochester, NY, since 1991, where he is a Distinguished Professor, the Director of the High Performance VLSI/IC Design and Analysis Laboratory, and the Director of the Center for Electronic Imaging Systems. He is also a Visiting Professor at the Technion–Israel Institute of Technology. His current research and teaching interests are in high-performance synchronous digital and mixed-signal microelectronic design and analysis with application to high-speed portable processors and low-power wireless communications. He is the author of more than 300 papers and book chapters, numerous patents, and the author or editor of nine books in the fields of high-speed and low-power CMOS design techniques, high-speed interconnect, and the theory and application of synchronous clock and power distribution networks.

Dr. Friedman is the Regional Editor of the Journal of Circuits, Systems and Computers, a member of the editorial boards of Analog Integrated Circuits and Signal Processing, Microelectronics Journal, Journal of Low Power Electronics, and Journal of VLSI Signal Processing, Chair of the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS steering committee, and a member of the technical program committee of a number of conferences. He previously was the Editor-in-Chief of the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, a member of the editorial board of the PROCEEDINGS OF THE IEEE and IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II: ANALOG AND DIGITAL SIGNAL PROCESSING, a member of the Circuits and Systems (CAS) Society Board of Governors, Program and Technical Chair of several IEEE conferences, and a receipient of the University of Rochester Graduate Teaching Award and College of Engineering Teaching Excellence Award. Dr. Friedman is a Senior Fulbright Fellow and an IEEE Fellow.

**Michael Sotman** received the B.S. and M.S. degrees in electrical engineering from Technion–Israel Institute of Technology, Haifa, Israel, in 1996 and 2007, respectively.

In 1995, he joined Intel Corporation, Israel Development Center in Haifa, where he is a Validation Engineer. His research interests are in power delivery and signal integrity.

**Avinoam Kolodny** (S'78–M'81) received the D.Sc. degree in microelectronics from Technion–Israel Institute of Technology, Haifa, Israel, in 1980.

He joined Intel Corporation, where he was engaged in diverse research and development activities related to device physics, VLSI circuits, and electronic design automation. In 2000, he joined the Electrical Engineering faculty at the Technion. His research interests are in VLSI systems and R&D methodologies.